-

Notifications

You must be signed in to change notification settings - Fork 571

Projects

LiteX is developed and used by Enjoy-Digital since 2012 to co-develop full-systems with our partners and provide an convenient and efficient solutions to create SoCs on FPGA based systems. Here are some of the last project we worked on with our partners:

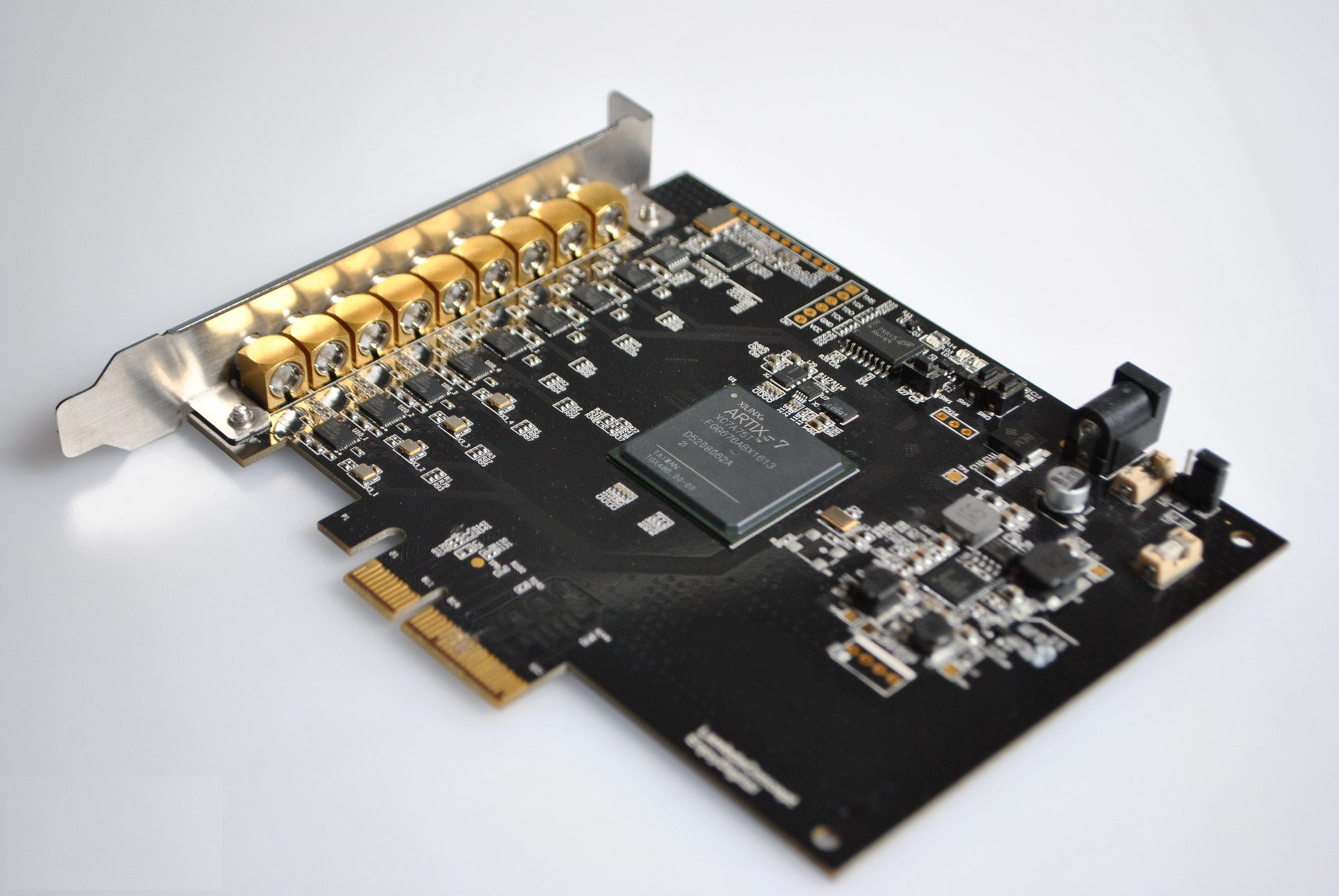

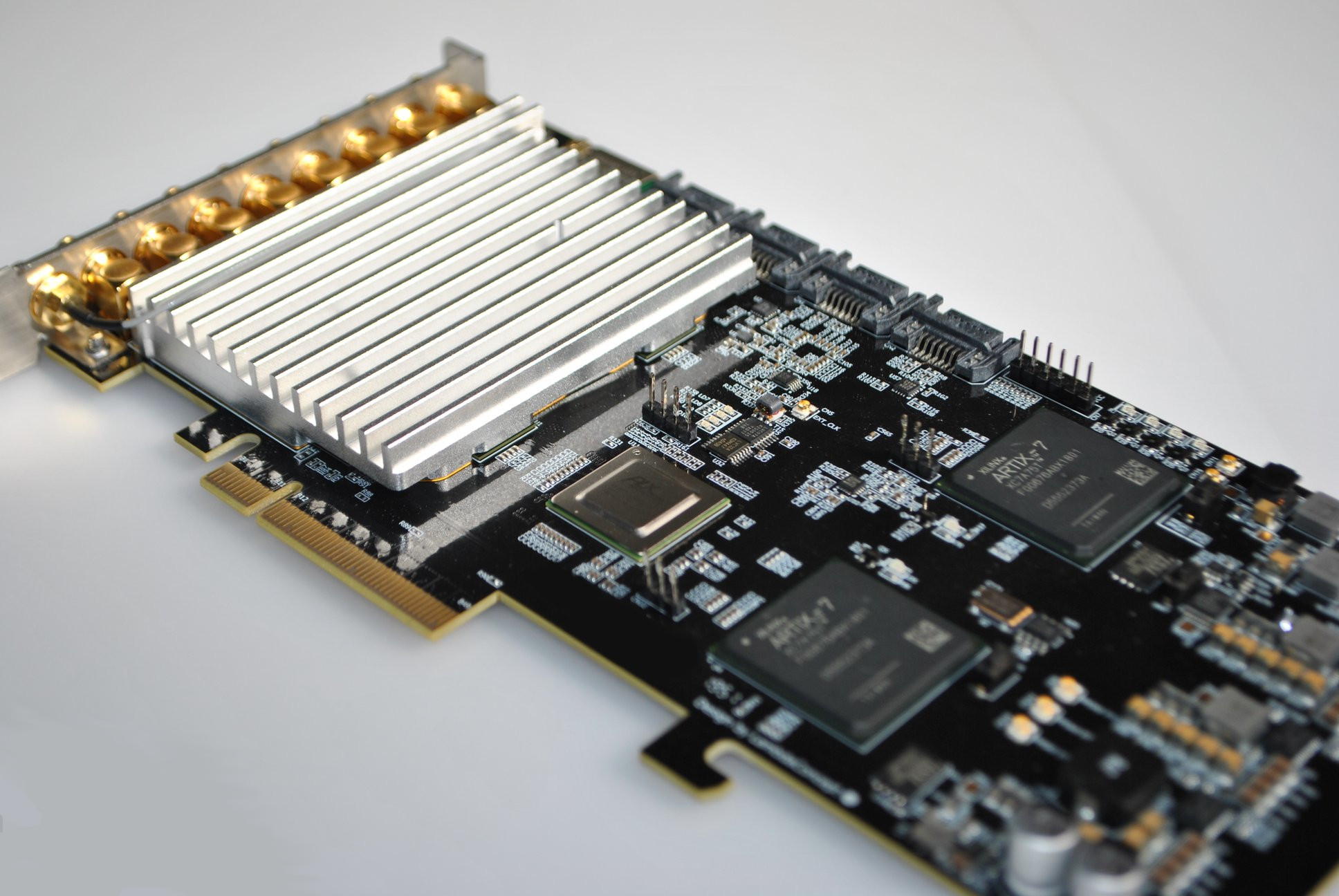

The SoC is built with LiteX, LitePCIe is used for the communication with the Host and LiteJESD204B is used between the AD937Xs and FPGAs.

The SoC is built with LiteX, LitePCIe is used to communicate with the Host and the Xilinx TripleRateSDI core is wrapped with custom datapath modules and gearboxes to make efficient use of the PCIe bus without any external buffering.

More projects can be found at Enjoy-Digital website.

Even if these projects are still unfortunately proprietary, LiteX has been originally developed to create these systems and most of the open-source features/cores come directly from these projects. Working on these systems allow us to keep track of the industry standards/constraints, force us to be practical, use efficient solutions and motivate us to continue improving the tools/adding new features, because that's what we like: creating systems!

Collections of projects with LiteX involved that could be useful for users to better understand LiteX, go further and/or find some inspiration.

The LiteX-Acorn-Baseboards are baseboards developed around the SQRL's Acorn board (or Nite/LiteFury) expanding their possibilities.

- Have an FPGA board with 32MB of RAM and want to test Linux on it?

- Want to study/explore a RISC-V Linux capable SoC?

- Want to create a full autonomous SoC with LiteX and its peripherals (SPI, I2C, SDCard, FrameBuffer, etc...) managed by Linux?

Linux-on-LiteX-VexRiscv project demonstrates how to create a Linux capable SoC with VexRiscv CPU, a 32-bits Linux Capable RISC-V CPU written in Spinal HDL. A SoC around the VexRiscv CPU is created using LiteX as the SoC builder and LiteX's cores written in Migen Python DSL (LiteDRAM, LiteEth, LiteSDCard). All the components used to create the SoC are open-source and the flexibility of Spinal HDL/Migen allow targeting easily very various FPGA devices/boards: Lattice, Altera, Xilinx, Microsemi FPGAs with SDRAM/DDR/DDR2/DDR3/DDR4 RAMs, RMII/MII/RGMII/1000BASE-X Ethernet PHYs. On Lattice ECP5 FPGAs, the open source toolchain allows creating full open-source SoC with open-source cores and toolchain!

This project demonstrates how high level HDLs (Spinal HDL, Migen) enable new possibilities and complement each other. Results shown there are the results of a productive collaboration between open-source communities.ant to test easily control LiteX cores.

The NeTV2 is a HDMI capture/playback board based on an Xilinx Artix7 FPGA.

The official SoC is doing an overlay (up to 1080p60) from the Raspberry Pi 3B+ on an HDMI stream with or without HDCP. The SoC of the Artix7 FPGA is built with LiteX, a VexRiscv CPU is used for the control, LiteDRAM as the DDR3 controller to store the CPU firmware and the do HDMI buffering and LiteVideo for the HDMI playback/capture.

The libre SoC makes use of the PCIe Gen2 X4 connector of the board with LitePCIe to create a HDMI capture/playback device.

The Fomu is a tiny FPGA board that fits in your USB port. The SoC of the FPGA is built with LiteX, a custom version of VexRiscv CPU is used for the control and the ValentyUSB core allows the board to communicate with the Host computer and emulate various USB devices. Fomu demonstrates how iCE40 designs can be tiny and powerful: Fomu can run Micropython/Zephyr on its RISC-V CPU while allowing software debug over GDB and gateware debug over the USB bridge and is able to reprogram itself directly from USB with Foboot. The Fomu Workshop workshop is also a great introduction to FPGA design.

Adding the Rocket Chip (64-bit RISC-V CPU) to the LiteX ecosystem, this project is capable of booting a nearly unmodified 64-bit upstream Linux kernel (with only the LiteEth network driver currently patched in).

Targeted toward the ECP5-5G-Versa and the TrellisBoard (but also known to work on the Nexys 4 DDR), the ultimate goal is to boot a Linux distro (e.g., Fedora), and use native riscv64 builds of the Libre FPGA toolchain (yosys/trellis/nextpnr) to build the underlying FPGA-based computer's own bitstream!

For the latest details, check out http://www.contrib.andrew.cmu.edu/~somlo/BTCP.

Betrusted is a protected place for your private matters. It’s built from the ground up to be checked by anyone, but sealed only by you. Betrusted is more than just a secure CPU – it is a system complete with screen and keyboard, because privacy begins and ends with the user.

Betrusted prototypes are built around two FPGAs SoC built with LiteX: The iCE40 based Embedded controller SoC and the Spartan7 based Secure Domain SoC.

Current solutions for USB3 connectivity with an FPGA require the use of an external SerDes chip (TI TUSB1310A - SuperSpeed 5 Gbps USB 3.0 Transceiver with PIPE and ULPI Interfaces) or external FIFO chip (FTDI FT60X or Cypress FX3). The aim of this project is to experiment with High Speed Transceivers (SERDES) of popular FPGAs to create a USB3.0 PIPE interface and see if it's possible to just use the transceivers of the FPGA for the USB3 connectivity and have the USB3 PIPE directly implemented in the fabric (and then avoid any external chip!)

The aim of this project is to create a PCIe interposer + FPGA capture board for PCIe signals capture and analysis with cheap hardware.

Chubby75 project documents cheap FPGA based led controllers (15$ shipping included) that can be repurposed as FPGA development boards with 2x 1Gbps interfaces / Spartan6 or ECP5 FPGAs / SDRAM, be used as GPIOs over network devices or for their original purpose: control led panels for a led cube :) LiteX and LiteEth have been tested on the reversed pinout and boards are supported in LiteX-boards.

Have a question or want to get in touch? Our IRC channel is #litex at irc.libera.chat.

- Welcome to LiteX

- LiteX's internals

- How to

- Create a minimal SoC-TODO

- Add a new Board-TODO

- Add a new Core-WIP

- Add a new CPU-WIP

- Reuse-a-(System)Verilog,-VHDL,-Amaranth,-Spinal-HDL,-Chisel-core

- Use LiteX on the Acorn CLE 215+

- Load application code the CPU(s)

- Use Host Bridges to control/debug a SoC

- Use LiteScope to debug a SoC

- JTAG/GDB Debugging with VexRiscv CPU

- JTAG/GDB Debugging with VexRiscv-SMP, NaxRiscv and VexiiRiscv CPUs

- Document a SoC

- How to (Advanced)